Insider Brief

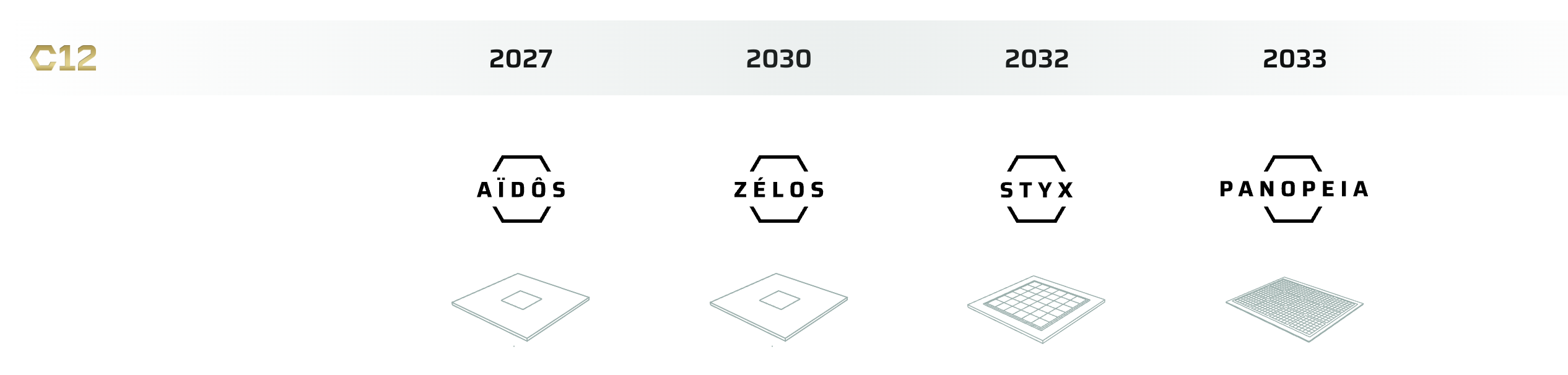

- C12 unveiled a multi-generation roadmap to build fault-tolerant quantum computers using carbon nanotube spin qubits, targeting utility-scale systems by 2033.

- The roadmap progresses from early logical qubits in Aïdôs (2027) to large-scale systems in Panopeia (2033), scaling to over 100,000 physical qubits and hundreds of logical qubits with improving error rates.

- The company’s approach emphasizes system architecture, modular chiplet-based integration, and efficient error correction rather than simply increasing qubit counts, aiming to enable scalable and deployable quantum systems.

PRESS RELEASE –C12, a Paris-based quantum computing company developing processors based on carbon nanotube spin qubits, today unveiled its technology roadmap towards commercial fault-tolerant quantum computing. The roadmap outlines four generations of systems, from Aïdôs (2027) to Panopeia (2033), designed to scale quantum processors from early logical qubits to utility-scale quantum computers.

The announcement reflects the company’s dedication to systems engineering and large-scale integration. Rather than focusing on increasing the number of qubits simplistically, C12 is addressing the architectural challenges that determine whether quantum computers can scale to useful levels. These include efficient error correction, scalable interconnects, reproducible manufacturing, and deployable system design.

“Our objective is not simply to build more qubits,” said Pierre Desjardins, co-founder and CEO of C12. “The real challenge is building quantum computers that can scale reliably. Our architecture is designed from the outset for scalability, speed, and real-world viability.”

C12’s roadmap introduces four processor generations.

- Aïdôs, expected in 2027, will demonstrate the company’s first logical quantum operations. The system will integrate 16 physical qubits to form a logical qubit while maintaining sub-microsecond physical gate speeds.

- Zélos, planned for 2030, introduces modular semiconductor integration. The processor will scale to 236 physical qubits and eight logical qubits while reducing logical error rates to approximately 10⁻⁵. This generation introduces chiplet packaging, cryogenic electronics, all-digital control signals, an on-chip qubit bias array, and multiplexed readout designed to support scalable manufacturing.

- Styx, targeted for 2032, extends the modular architecture by replicating the chiplet unit of Zélos many times. The processor is designed to reach 8,500 physical qubits and at least 128 logical qubits, with logical error rates of 10⁻⁶ and significantly improved power efficiency.

- Panopeia, planned for 2033, represents the transition to an integrated utility-scale quantum system, capable of supporting universal quantum computation. The architecture combines Styx modules to target more than 100,000 physical qubits and nearly 800 logical qubits, reducing logical error rates to around 10⁻⁷ while maintaining sub-watt power consumption per qubit within a single cryostat.

C12’s processors use carbon nanotube spin qubits, a solid-state platform that combines the speed of semiconductor devices with strong noise isolation. Ultra-pure carbon-12 nanotubes provide a nearly ideal one-dimensional pathway for electrical signals, enabling fast electronic gate operations and uniform qubit control.

“The materials platform we use gives us an unusual combination of speed, connectivity, and stability,” said Matthieu Desjardins, chairman, co-founder, and CTO of C12. “That allows us to design systems where quantum error correction and large-scale integration are efficient at scale.”

The architecture incorporates a quantum bus enabling all-to-all connectivity within qubit zones and relies on chiplet-based 3D integration to scale processors through modular replication. The company also targets a fully-scaled system within a 17 square meter footprint and sub-watt power consumption per qubit in order to keep large-scale quantum systems practical to deploy.

The systems in the roadmap are named after figures from Greek mythology, reflecting both the progression of the technology and the philosophical roots of science in ancient Greece. Aïdôs, the spirit of humility, reflects the fact this system targets only the first small step toward utility: a modest logical qubit. Zélos, the embodiment of ambition, represents the drive to scale the quantum system while maintaining fidelity and control. Styx, the goddess overseeing the mythological river separating worlds, symbolizes the boundary between the classical world and the world of potential quantum advantage as the hardware becomes resilient enough to support large-scale computation. Panopeia, a name that reflects the ability to see all possibilities, much like qubits, represents C12’s vision of a useful fault-tolerant quantum processor operating at utility scale.

C12 develops its technology stack in its laboratory in central Paris, including materials, nanofabrication, and system architecture.