Insider Brief

- Researchers have developed the Collision Clustering (CC) decoder, a hardware-based quantum error decoder capable of megahertz-level speeds, meeting the demands of next-generation quantum computers.

- The CC decoder efficiently corrects errors in quantum systems using FPGA and ASIC hardware, decoding up to 1,057 qubits with minimal power consumption and small physical footprints suitable for cryogenic environments.

- The CC decoder is another example of the progress made in robust quantum error correction, which will be vital to reach fault-tolerant scale quantum computing.

Researchers from Riverlane report they have developed a hardware-based quantum error decoder that meets the demanding speed and efficiency requirements of next-generation quantum computers, according to a just published paper in Nature Electronics.

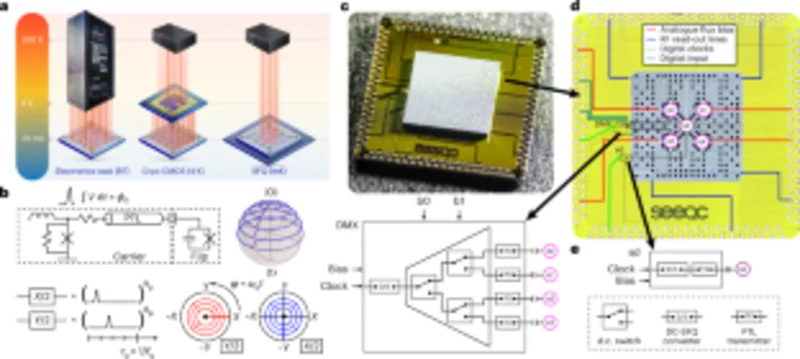

In the study, the team members detail that their Collision Clustering (CC) decoder achieves megahertz-level decoding speeds essential for handling errors in large-scale quantum systems. By implementing the decoder on field-programmable gate arrays (FPGAs) and application-specific integrated circuits (ASICs), the team demonstrated the ability, in certain platforms, to decode up to 1,057 qubits with unprecedented efficiency, take a step toward practical fault-tolerant quantum computing.

The team writes that the introduction of the decoder also marks a key step along their quantum error control (QEC) roadmap.

“Today’s publication in Nature Electronics is a proud moment,” the team writes in a LinkedIn post. “With QEC implementation now a top priority for every quantum computer and control system maker, we look forward to driving the continued progress of our QEC roadmap through 2025 and beyond.”

They also added that to the best of their current knowledge the Collision Clustering (CC) decoder was the most powerful in the world.

The Fragility of Qubits

Quantum computers rely on qubits, which are highly sensitive to their environment. Small disturbances can introduce errors, making quantum systems fragile and error-prone. QEC protocols offer a solution by encoding logical qubits using a larger number of physical qubits. However, implementing QEC requires a decoder capable of analyzing a constant stream of error signals, known as syndrome data, and applying corrections in real time.

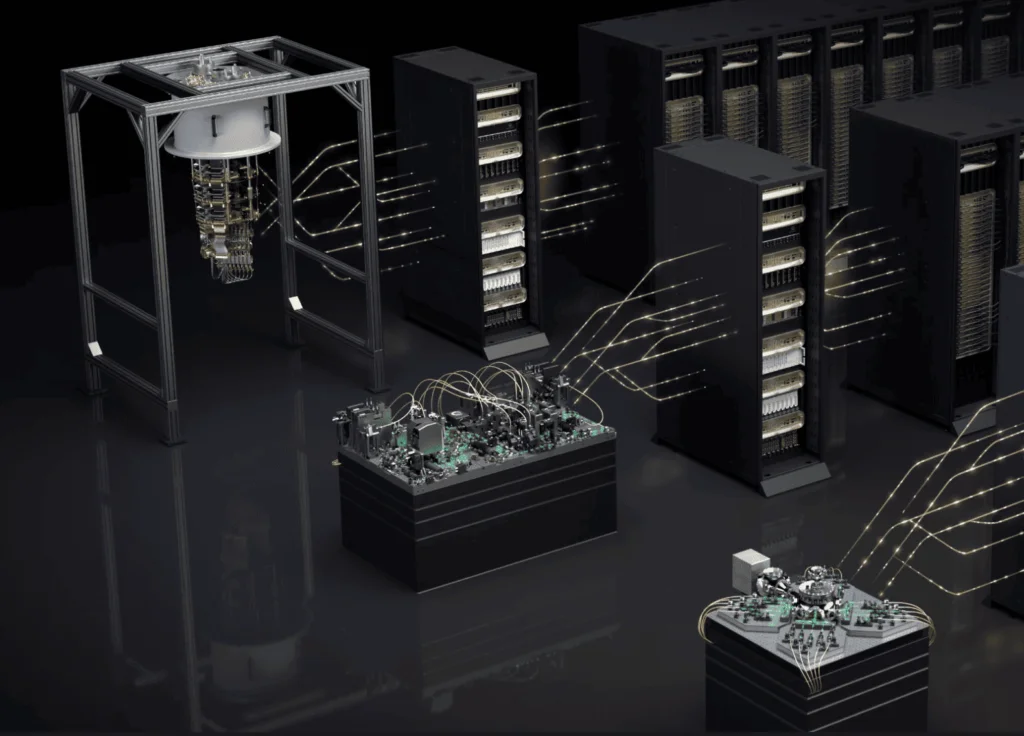

The challenge lies in scaling these decoders for larger quantum systems. Current software-based solutions are either too slow or consume excessive computational resources. Hardware-based decoders provide a potential solution but must balance speed, power consumption, and resource efficiency. The CC decoder addresses these issues, offering a scalable, hardware-efficient solution for future quantum computers.

According to the paper, the CC decoder was tested on two platforms: an FPGA prototype and a custom-designed ASIC. Both implementations achieved decoding speeds exceeding one million cycles per second, a key threshold for practical QEC in superconducting qubits. The FPGA implementation processed an 881-qubit surface code in 810 nanoseconds, while the ASIC handled a 1,057-qubit surface code in just 240 nanoseconds. These speeds align with the megahertz syndrome generation rates of modern quantum processors.

In terms of resource efficiency, the ASIC occupies only 0.06 square millimeters of chip area and consumes a mere 8 milliwatts of power — well within the constraints of cryogenic environments where quantum computers operate. The FPGA implementation also demonstrated impressive efficiency, using just 4.5% of its available computational elements for large-scale decoding tasks.

A Critical Milestone

Fault-tolerant quantum computing, the ability to perform reliable computations despite errors, is a critical milestone for the field. Practical quantum computers capable of solving real-world problems will require thousands, if not millions, of qubits. Without an efficient decoding system, these machines would suffer from crippling delays, rendering them ineffective.

The CC decoder provides a path forward by meeting stringent speed and efficiency requirements while maintaining scalability. Its hardware implementation is particularly significant for cryogenic quantum systems, where power budgets are limited to prevent overheating. The ASIC design’s low power consumption ensures that decoders can be tightly integrated with quantum control systems, enabling real-time error correction at scale.

The researchers write: “Fault-tolerant quantum computing requires a decoder to process error syndromes at speed to prevent a decoding backlog that exponentially slows down the logical clock rate. Any scalable quantum computer also requires a decoder to be resource efficient, which will allow tight integration with control systems in a cryogenic environment. To meet these requirements, we designed CC to be memory and power efficient.”

How It Works

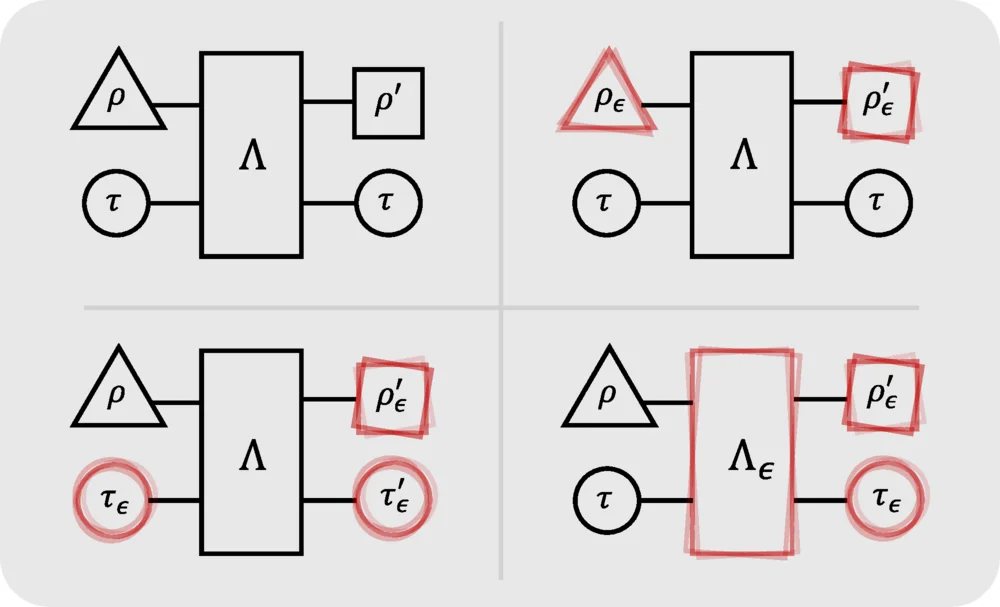

The CC decoder uses an optimized version of the Union-Find algorithm — an algorithm that efficiently groups and merges related data — to identify and correct errors in quantum systems. In this case, the algorithm groups error signals, or defects, into clusters. These clusters are then analyzed to determine the necessary corrections, which are applied in subsequent operations.

The researchers introduced several innovations to improve the algorithm’s performance. A novel memory structure, the cluster growth stack (CGS), efficiently tracks the state of growing clusters. This approach reduces resource usage compared to traditional methods while maintaining the required decoding speed. For the ASIC implementation, additional design optimizations allowed the decoder to fit within a tiny chip area while consuming minimal power.

The decoder was tested using the surface code, a leading QEC scheme known for its robustness and scalability. By simulating a realistic noise model, the team demonstrated the CC decoder’s ability to handle the complexities of real-world quantum systems.

Limitations

The team indicates that the CC decoder has some areas that will require further investigation to reach full usage. The study primarily focused on simulated logical memory experiments, which preserve quantum states for finite durations. For long-term fault-tolerant operations, continuous real-time decoding will be required. The researchers acknowledged that their decoder does not yet support sliding window decoding, a technique necessary for maintaining logical states indefinitely.

While the CC decoder’s nonlinear scaling is mitigated by parallelization, further improvements may also be needed for extremely large quantum systems. The researchers identified bottlenecks in the collision detection process, particularly for high-density error scenarios, and outlined plans to address these issues in future iterations.

Refine and Improve

The researchers plan to refine the CC decoder’s architecture to improve performance further and expand its capabilities. Sliding window decoding, which processes a rolling set of error signals to enable continuous error correction, is a key area of focus. They also aim to test the decoder in real-world cryogenic environments, integrating it with complementary metal-oxide semiconductor (CMOS) control systems.

Another goal is to enhance the decoder’s efficiency for even larger quantum systems. By optimizing memory usage and improving algorithmic scaling, the team hopes to support utility-scale quantum computers capable of tackling complex problems in fields such as cryptography, materials science and artificial intelligence.

Beyond The Decoder

The development of efficient hardware decoders like the CC decoder marks a significant step toward practical quantum computing. By addressing key challenges in speed, scalability, and power consumption, the research provides a blueprint for integrating QEC systems into future quantum processors.

Riverlane reports that they are already working on the next big step.

They write in the post: “The next big milestone? Using real-time QEC to achieve a ‘MegaQuOp’ (one million error-free quantum operations). This is where quantum computing’s first practical use cases beyond the supercomputing threshold will begin to emerge.”

For a deeper, more technical dive — which this article can’t provide — please read the paper here.

The researcher team included Ben Barber, Kenton M. Barnes, Tomasz Bialas, Okan Buğdaycı, Earl T. Campbell, Neil I. Gillespie, Kauser Johar, Ram Rajan, Adam W. Richardson, Luka Skoric, Canberk Topal, Mark L. Turner and Abbas B. Ziad, all of Riverlane. Campbell is also affiliated withthe University of Sheffield.